## UNIVERSITÀ DEGLI STUDI DI TRIESTE

## Joint-supervision with Universidad Nacional de San Luis

XXXV Ciclo del Dottorato di Ricerca in Ingegneria Industriale e dell'Informazione

Doctorado en Ciencias de la Computación

PO FRIULI VENEZIA GIULIA - FONDO SOCIALE EUROPEO 2014/2020

# SoC-based FPGA architecture for image analysis

## and other highly demanding applications

Settore scientifico-disciplinare: ING-INF/01 Electronics

Dottoranda:

Coordinatore:

Supervisori di tesi:

Giovanni Ramponi

Alberto Tessarolo

Verónica Gil Costa

Co-supervisore di tesi: María Liz Crespo

Anno accademico 2021/2022

Romina Soledad Molina

"You will begin to touch heaven, Jonathan, at the moment that you touch perfect speed. And that isn't flying a thousand miles an hour, or a million, or flying at the speed of light. Because any number is a limit, and perfection doesn't have limits. Perfect speed, my son, is being there."

- Jonathan Livingston Seagull - Richard Bach

### Acknowledgment

Grazie a Dio perché la sua energia è sempre presente, in ogni passo.

Grazie ai miei supervisori, Gianni, Liz, e Verónica, che sono stati presenti durante tutto questo tempo, guidando la barca che oggi mi ha permesso di raggiungere la meta di questo viaggio. Grazie per aver nutrito il mio cammino con la sua saggezza e la lora buona qualità umana. Grazie anche ad Andrés, che mi ha dato il suo sostegno in questa parte del viaggio.

Grazie alle istituzioni che mi hanno permesso di sviluppare il mio dottorato: Università degli Studi di Trieste, The Abdus Salam International Centre for Theoretical Physics, Consiglio Nazionale delle Ricerche, Universidad Nacional de San Luis.

Grazie eterne alla mia famiglia, perché anche a distanza fisica sono sempre presenti, con tutto l'amore, il supporto, e la comprensione. Grazie per essere sempre al mio fianco. Vi volgio tanto bene!

Andrea una volta mi ha detto che i supervisori sono come il capitano della nave, ci guidano in questo processo di apprendimento che attraversa ogni ambito della nostra vita. Grazie infinite essere presente, per avermi permesso d'imparare dalla tua saggezza.

Grazie Raffaele, Franco e Salvatore, per avermi accompagnato in questi anni.

Grazie a Iván, Werner, Charm Loong, Luis, Bruno, Maynor, e Agustín per avermi accompagnato in tutti questi anni, per l'amicizia, le risate, i momenti di lavoro, e quelli di relax.

Grazie a tutti i miei amici dell'anima che vibrano nell'eternità dell'esistenza.

Infinitamente, grazie al mare!

Romina Soledad Molina

#### Summary

Nowadays, the development of algorithms focuses on performance-efficient and energy-efficient computations. Technologies such as field programmable gate array (FPGA) and system on chip (SoC) based on FPGA (FPGA/SoC) have shown their ability to accelerate intensive computing applications while saving power consumption, owing to their capability of high parallelism and reconfiguration of the architecture.

Currently, the existing design cycles for FPGA/SoC are time-consuming, owing to the complexity of the architecture. Therefore, to address the gap between applications and FPGA/SoC architectures and to obtain an efficient hardware design for image analysis and highly demanding applications using the high-level synthesis tool, two complementary strategies are considered: ad-hoc techniques and performance estimator.

Regarding ad-hoc techniques, three highly demanding applications were accelerated through HLS tools: pulse shape discriminator for cosmic rays, automatic pest classification, and re-ranking for information retrieval, emphasizing the benefits when this type of applications are traversed by compression techniques when targeting FPGA/SoC devices.

Furthermore, a comprehensive performance estimator for hardware acceleration is proposed in this thesis to effectively predict the resource utilization and latency for FPGA/SoC, building a bridge between the application and architectural domains. The tool integrates analytical models for performance prediction, and a design space explorer (DSE) engine for providing high-level insights to hardware developers, composed of two independent sub-engines: DSE based on singleobjective optimization and DSE based on evolutionary multi-objective optimization.

### Riassunto

Al giorno d'oggi, lo sviluppo di algoritmi si concentra su calcoli efficienti in termini di prestazioni ed efficienza energetica. Tecnologie come il field programmable gate array (FPGA) e il system on chip (SoC) basato su FPGA (FPGA/SoC) hanno dimostrato la loro capacità di accelerare applicazioni di calcolo intensive risparmiando al contempo il consumo energetico, grazie alla loro capacità di elevato parallelismo e riconfigurazione dell'architettura.

Attualmente, i cicli di progettazione esistenti per FPGA/SoC sono lunghi, a causa della complessità dell'architettura. Pertanto, per colmare il divario tra le applicazioni e le architetture FP-GA/SoC e ottenere un design hardware efficiente per l'analisi delle immagini e altri applicazioni altamente demandanti utilizzando lo strumento di sintesi di alto livello, vengono prese in considerazione due strategie complementari: tecniche ad hoc e stima delle prestazioni.

Per quanto riguarda le tecniche ad-hoc, tre applicazioni molto impegnative sono state accelerate attraverso gli strumenti HLS: discriminatore di forme di impulso per i raggi cosmici, classificazione automatica degli insetti e re-ranking per il recupero delle informazioni, sottolineando i vantaggi quando questo tipo di applicazioni viene attraversato da tecniche di compressione durante il targeting dispositivi FPGA/SoC.

Inoltre, in questa tesi viene proposto uno stimatore delle prestazioni per l'accelerazione hardware per prevedere efficacemente l'utilizzo delle risorse e la latenza per FPGA/SoC, costruendo un ponte tra l'applicazione e i domini architetturali. Lo strumento integra modelli analitici per la previsione delle prestazioni e un motore design space explorer (DSE) per fornire approfondimenti di alto livello agli sviluppatori di hardware, composto da due motori indipendenti: DSE basato sull'ottimizzazione a singolo obiettivo e DSE basato sull'ottimizzazione evolutiva multiobiettivo.

iv

# Contents

|   | Ack  | nowledgment                                                         | ii  |

|---|------|---------------------------------------------------------------------|-----|

|   | Sun  | mary                                                                | iii |

|   | Rias | sunto                                                               | iv  |

|   | Turk |                                                                     |     |

| 1 | Intr | oduction                                                            | 1   |

|   | 1.1  | Motivation                                                          | 1   |

|   | 1.2  | Hypothesis                                                          | 3   |

|   | 1.3  | Objectives                                                          | 3   |

|   |      | 1.3.1 Specific objectives                                           | 4   |

|   | 1.4  | Contribution                                                        | 4   |

|   | 1.5  | Methodology                                                         | 5   |

|   | 1.6  | Challenges                                                          | 7   |

|   | 1.7  | Scientific publications                                             | 10  |

|   | 1.8  | Thesis outline                                                      | 13  |

| 2 | Spe  | cific topics in machine learning and mathematical optimization      | 15  |

|   | 2.1  | Deep neural networks                                                | 15  |

|   | 2.2  | Compression for ML-based models                                     | 17  |

|   | 2.3  | Methodology to deploy DNN-based classifiers on SoC                  | 18  |

|   | 2.4  | Mathematical optimization                                           | 21  |

|   |      | 2.4.1 Bayesian optimization                                         | 22  |

|   |      | 2.4.2 Multi-objective optimization based on evolutionary algorithms | 23  |

| 3 | Bac  | kground on SoC-based FPGA and parallel models                       | 25  |

|   | 3.1  | SoC-based FPGA                                                      | 25  |

|   |      | 3.1.1          | Design space exploration and metrics                                            | 26 |

|---|------|----------------|---------------------------------------------------------------------------------|----|

|   |      | 3.1.2          | Improving performance with HLS tool                                             | 28 |

|   | 3.2  | Parall         | el computing models for performance estimation                                  | 31 |

|   |      | 3.2.1          | Random access machine and parallel random access machine $\ldots \ldots \ldots$ | 31 |

|   |      | 3.2.2          | Bulk Synchronous Parallel model                                                 | 32 |

|   |      | 3.2.3          | LogP model                                                                      | 34 |

|   |      | 3.2.4          | Collective Computing Model                                                      | 34 |

|   |      | 3.2.5          | Roofline Model                                                                  | 35 |

|   | 3.3  | Sumn           | nary                                                                            | 36 |

| 4 | Stat | e of th        | e art in performance estimators for SoC-based FPGA                              | 38 |

|   | 4.1  | Perfor         | rmance estimation for FPGA                                                      | 38 |

|   |      | 4.1.1          | General approaches                                                              | 39 |

|   |      | 4.1.2          | Design space exploration                                                        | 42 |

|   |      | 4.1.3          | Discussion                                                                      | 48 |

|   | 4.2  | Estim          | ators for highly demanding applications                                         | 52 |

|   |      | 4.2.1          | Models                                                                          | 52 |

|   |      | 4.2.2          | Frameworks                                                                      | 54 |

|   | 4.3  | Sumn           | nary of the chapter                                                             | 57 |

| 5 | MA   | RTE <b>: A</b> | comprehensive hardware acceleration performance estimator                       | 59 |

|   | 5.1  | MAR            | ГЕ general flow                                                                 | 59 |

|   | 5.2  | Initial        | lization stage                                                                  | 61 |

|   | 5.3  | Cost I         | Model                                                                           | 61 |

|   |      | 5.3.1          | Latency model                                                                   | 63 |

|   |      | 5.3.2          | Resource model                                                                  | 67 |

|   | 5.4  | Desig          | n space explorer                                                                | 70 |

|   |      | 5.4.1          | Single-objective Bayesian optimization                                          | 71 |

|   |      | 5.4.2          | Evolutionary multi-objective optimization (EMO)                                 | 72 |

|   |      | 5.4.3          | Rules for guiding the DSE engine                                                | 74 |

|   | 5.5  | Outpu          | ıts                                                                             | 74 |

|   | 5.6  | Sumn           | nary of the chapter                                                             | 75 |

| 6 | Ima | ige ana | lysis and highly demanding applications               | 76  |

|---|-----|---------|-------------------------------------------------------|-----|

|   | 6.1 | Image   | e analysis and other highly demanding applications    | 76  |

|   | 6.2 | Pulse   | shape discrimination for cosmic rays                  | 77  |

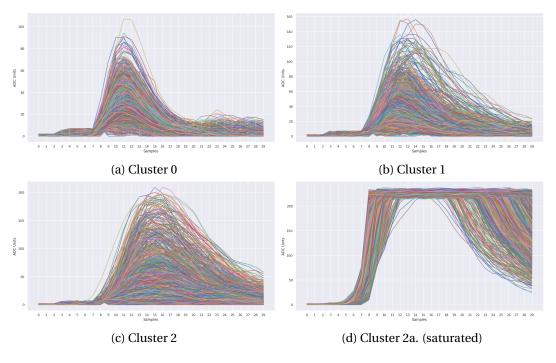

|   |     | 6.2.1   | Dataset                                               | 78  |

|   |     | 6.2.2   | ML-based architecture                                 | 79  |

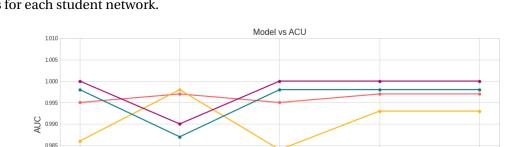

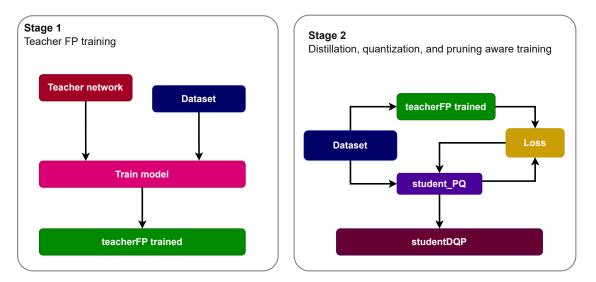

|   |     | 6.2.3   | ML-based model compression                            | 81  |

|   |     | 6.2.4   | Implementation results                                | 82  |

|   | 6.3 | Autor   | natic pest classification based on CNN                | 84  |

|   |     | 6.3.1   | ML-based architecture                                 | 85  |

|   |     | 6.3.2   | Dataset                                               | 86  |

|   |     | 6.3.3   | CNN assessment                                        | 87  |

|   |     | 6.3.4   | Implementation results                                | 88  |

|   | 6.4 | Re-ra   | nking algorithm                                       | 88  |

|   |     | 6.4.1   | Information retrieval system                          | 89  |

|   |     | 6.4.2   | Re-ranking through an ensemble of decision trees      | 89  |

|   |     | 6.4.3   | Towards the hardware implementation                   | 91  |

|   | 6.5 | Sumn    | nary of the chapter                                   | 94  |

| 7 | Exp | erime   | nts and results                                       | 96  |

|   | 7.1 | Exper   | imental setup                                         | 96  |

|   | 7.2 | Metri   | cs                                                    | 97  |

|   | 7.3 | Basic   | applications                                          | 98  |

|   | 7.4 | MAR     | ΓE performance evaluation                             | 99  |

|   |     | 7.4.1   | Analytical models for resource and latency estimation | 99  |

|   |     | 7.4.2   | Pulse shape discriminator: performance estimation     | 102 |

|   |     | 7.4.3   | Automatic pest classification: performance estimation | 103 |

|   |     | 7.4.4   | Re-ranking algorithm: performance estimation          | 105 |

|   |     | 7.4.5   | Discussion                                            | 106 |

|   | 7.5 | Asses   | sment of MARTE DSE engine                             | 106 |

|   |     | 7.5.1   | Assessment of the DSE engine based on BO              | 107 |

|   |     | 7.5.2   | Assessment of the DSE engine based on EMO             | 109 |

|    | 7.6   | MARTE runtime analysis                       | 13 |

|----|-------|----------------------------------------------|----|

|    | 7.7   | MARTE compatibility analysis                 | 14 |

|    | 7.8   | Summary of the chapter                       | 16 |

| 8  | Inte  | gration of MARTE with the state of the art 1 | 18 |

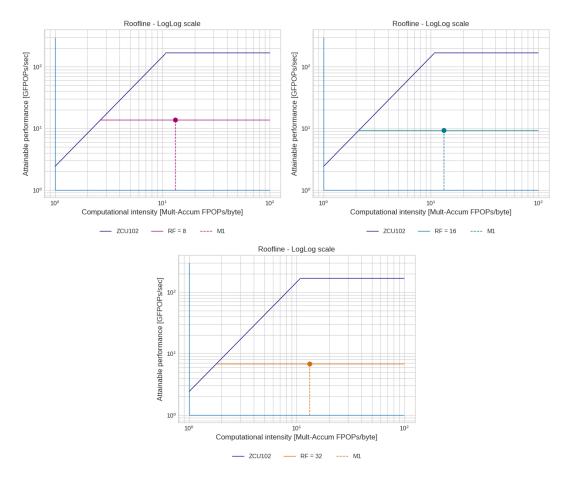

|    | 8.1   | Roofline Model                               | 18 |

|    |       | 8.1.1 Pulse shape discriminator              | 19 |

|    | 8.2   | Discussion                                   | 24 |

|    | 8.3   | Summary of the chapter                       | 24 |

| 9  |       |                                              | 25 |

|    | 9.1   | Future directions                            | 27 |

| Bi | bliog | raphy 12                                     | 29 |

# **List of Figures**

| 1.1 | Methodology.                                                                               | 5  |

|-----|--------------------------------------------------------------------------------------------|----|

| 2.1 | Detail of a single neuron function.                                                        | 16 |

| 2.2 | Knowledge distillation process.                                                            | 18 |

| 2.3 | Methodology. The input is the labeled dataset used to train the teacher and student        |    |

|     | (or target) networks. After this, the data structure generated is the input for the hls4ml |    |

|     | package, translating the neural network-based model into a HLS project. $\ldots$ .         | 19 |

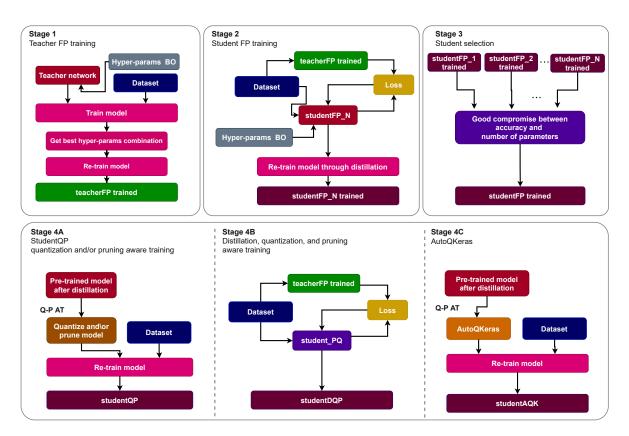

| 2.4 | Compression workflow to deploy DN classifiers on FPGA/SoC.                                 | 20 |

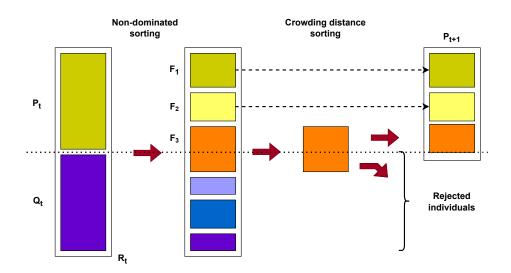

| 2.5 | General flow diagram of the NSGA-II algorithm.                                             | 24 |

| 3.1 | Architectures for Zynq-7000 SoC and Zynq UltraScale+ MPSoc devices                         | 26 |

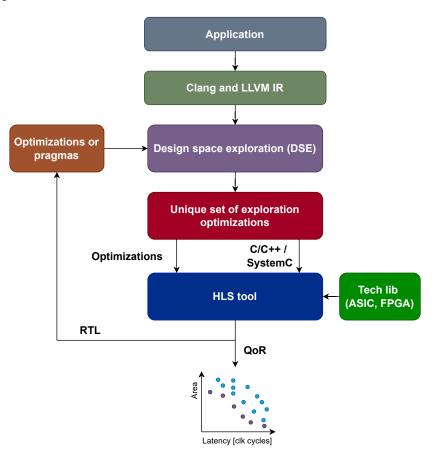

| 3.2 | Typical DSE framework with HLS in the loop.                                                | 28 |

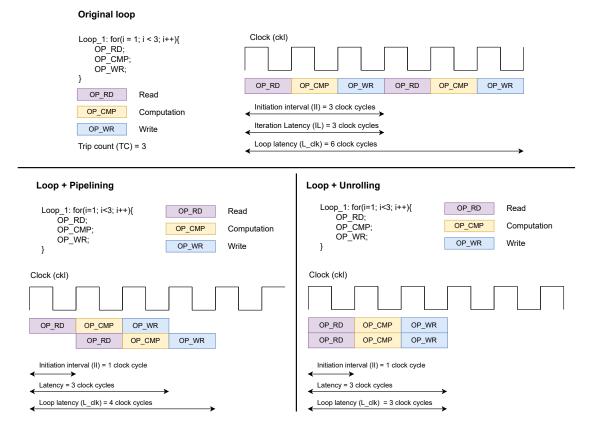

| 3.3 | HLS directives for loop handling.                                                          | 30 |

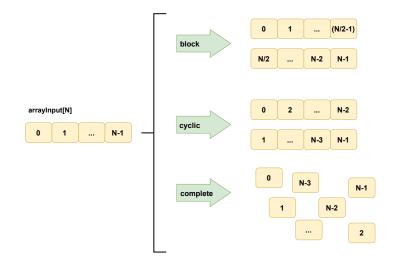

| 3.4 | HLS directives for memory optimization.                                                    | 30 |

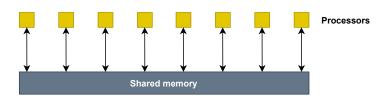

| 3.5 | PRAM model. Different processors execute read and write operations in a shared             |    |

|     | memory                                                                                     | 32 |

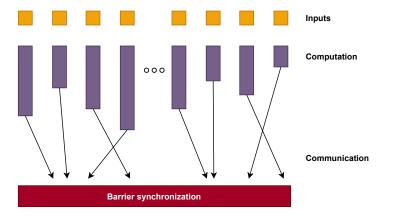

| 3.6 | Superstep of the BSP model.                                                                | 32 |

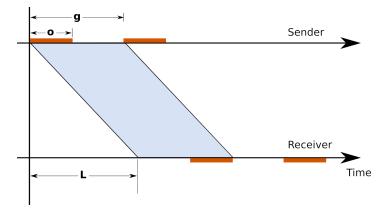

| 3.7 | LogP model. From a local point of view, for one Processor $(P)$ , g represents the gap     |    |

|     | between messages, $o$ is the communication overhead, and $L$ is the communication          |    |

|     | delay                                                                                      | 34 |

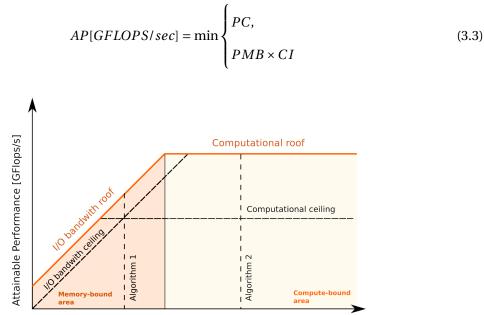

| 3.8 | Roofline model. The <i>x</i> -axis represents the operational or computational intensity |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | (CI) and y-axis represents the attainable performance (AP) or throughput. Computa-       |    |

|     | tional roof and I/O bandwidth roof limit the achievable AP. On the right (yellow area),  |    |

|     | the algorithms are compute-bound, while on the left (orange area), they are memory-      |    |

|     | bound                                                                                    | 35 |

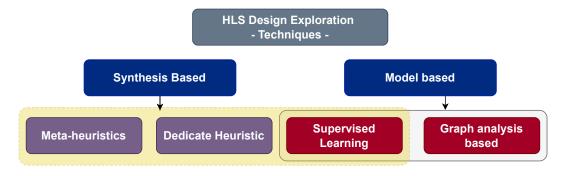

| 4.1 | Classification of HLS DSE techniques.                                                    | 43 |

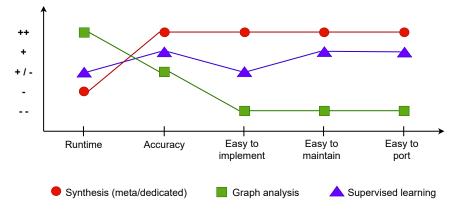

| 4.2 | Value curve for DSE                                                                      | 43 |

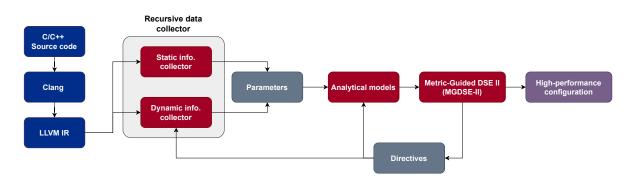

| 4.3 | COMBA framework overview. LLVM IR is extracted from the source code. This trace          |    |

|     | is the input for the recursive data collector, which will extract the parameters used by |    |

|     | the analytical models (latency and resource). MGDSE-II evaluates the configuration       |    |

|     | and defines the next set of directives to be applied. The output of the complete flow    |    |

|     | is the high-performance configuration.                                                   | 46 |

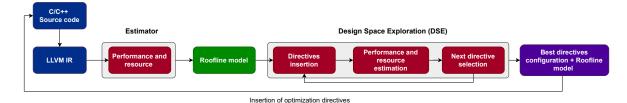

| 4.4 | DSE methodology based on Roofline. The input source code is translated to LLVM           |    |

|     | IR trace, obtaining the baseline for performance estimation and resource utilization.    |    |

|     | Subsequently, the Roofline model chart estimates memory bottlenecks. An auto-            |    |

|     | mated DSE phase allows resource and performance estimations, and the best feasible       |    |

|     | design is plotted along with the original Roofline chart.                                | 47 |

| 4.5 | Prospector framework. The inputs are the source code, clock frequency, and direc-        |    |

|     | tives; and the outputs are the synthesized designs with a trade-off between latency      |    |

|     | and area. The directives are encoded and sent to the BOU. Source code and clock fre-     |    |

|     | quency are the inputs for HLS Tools. Performance and cost values are obtained from       |    |

|     | HLS tool and Place & Route process                                                       | 48 |

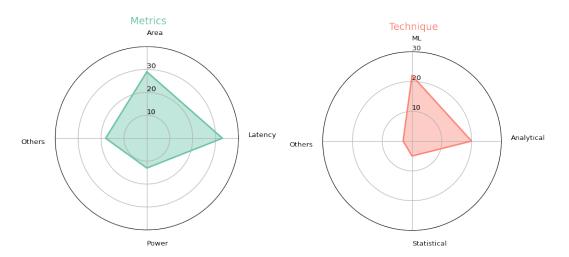

| 4.6 | Radar plots. (1) Metrics. (2) Techniques                                                 | 50 |

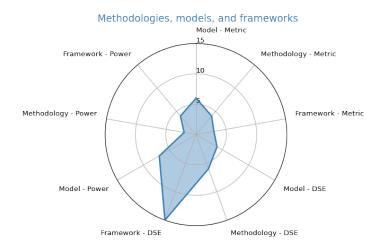

| 4.7 | Radar plot for models, methodologies, and frameworks for metric estimation, FPGA-        |    |

|     | based DSE, and power consumption.                                                        | 51 |

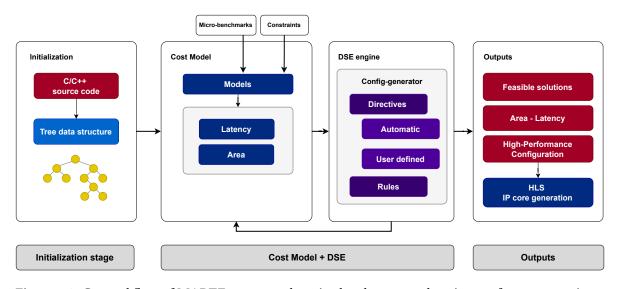

| 5.1 | General flow of MARTE, a comprehensive hardware acceleration performance esti-           |    |

|     | mator                                                                                    | 60 |

| 5.2 | Input of MARTE: source code as tree data structure.                                      | 61 |

| 5.3 | Terminology for a loop (without directives).                                             | 63 |

| 5.4 | Model for latency estimation.                                                            | 64 |

| 5.5  | Resource utilization model.                                                              | 67  |

|------|------------------------------------------------------------------------------------------|-----|

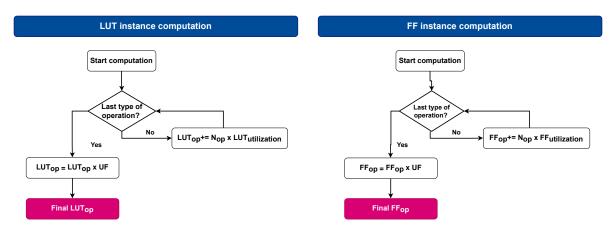

| 5.6  | Flow chart for LUT and FF computation due to operations.                                 | 68  |

| 5.7  | Steps involved in LUT and FF computation through multiple linear regression. $\ldots$    | 69  |

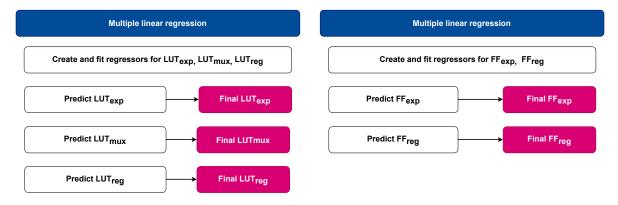

| 5.8  | Flow diagram of the single-objective BO for DSE.                                         | 72  |

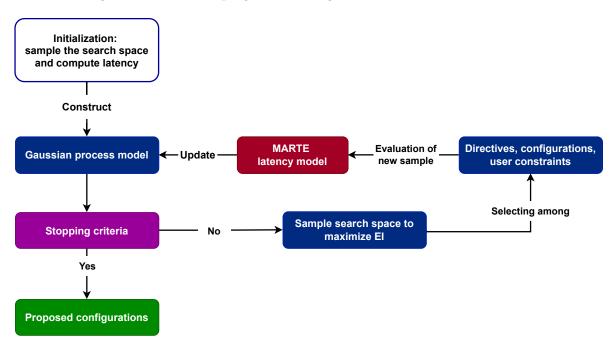

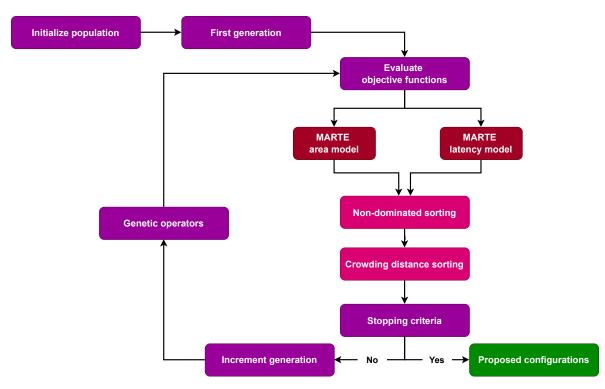

| 5.9  | Flow diagram of the EMO for DSE with NSGA-II solver.                                     | 73  |

| 6.1  | Cosmic rays DAQ system for Water Cherenkov Detectors.                                    | 78  |

| 6.2  | Samples of raw pulse traces of each cluster.                                             | 79  |

| 6.3  | MLP teacher architecture.                                                                | 80  |

| 6.4  | AUC per class for each student network.                                                  | 81  |

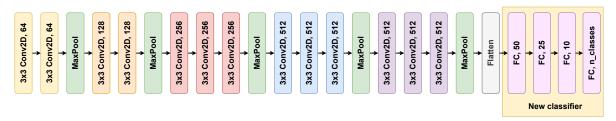

| 6.5  | Methodology for compression.                                                             | 85  |

| 6.6  | Teacher architecture based on VGG16, including the new classifier.                       | 85  |

| 6.7  | Distilled architecture.                                                                  | 86  |

| 6.8  | Samples of Pest24 dataset                                                                | 86  |

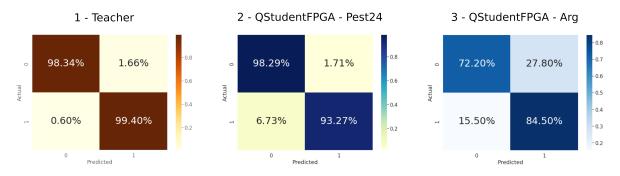

| 6.9  | Confusion matrix: VGG-16-based teacher (1), QStudentFPGA Pest24 dataset (2), QS-         |     |

|      | tudentFPGA ARG dataset (3)                                                               | 87  |

| 6.10 | Information retrieval.                                                                   | 89  |

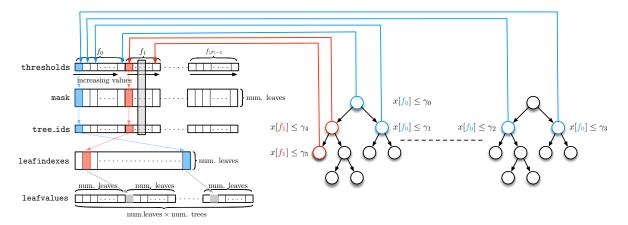

| 6.11 | Data layout of the QS algorithm.                                                         | 90  |

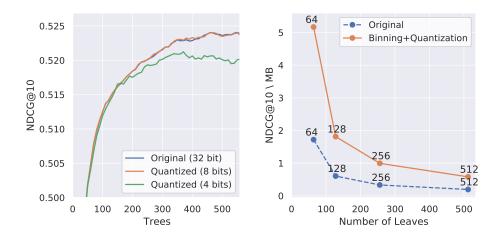

| 6.12 | $\lambda$ -MART efficiency/effectiveness trade-off. Right: NDCG@10 per MB of model size. |     |

|      | Left: impact of quantization on NDCG@10                                                  | 93  |

| 6.13 | High-level representation of the QS IP core.                                             | 93  |

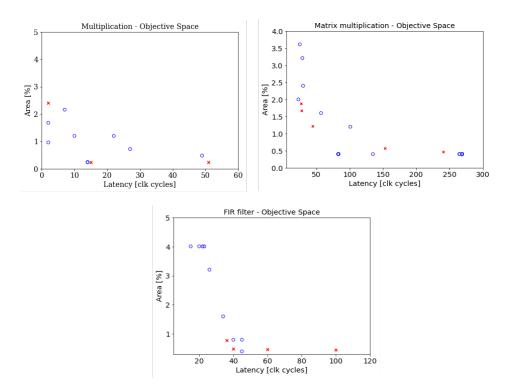

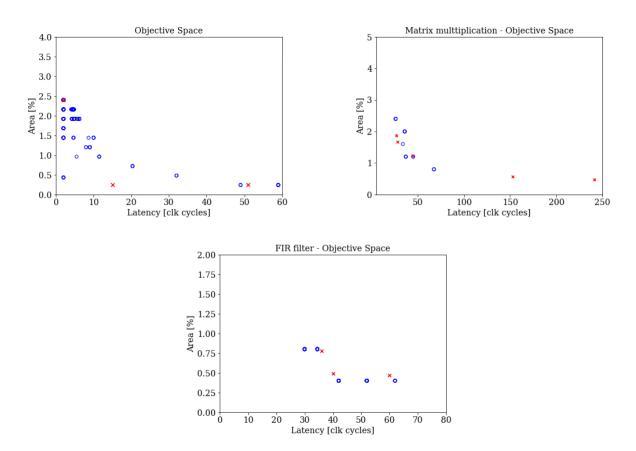

| 7.1  | DSE based on BO. Objective space for multiplication, matrix multiplication, and FIR      | 100 |

| 7.0  | filter.                                                                                  |     |

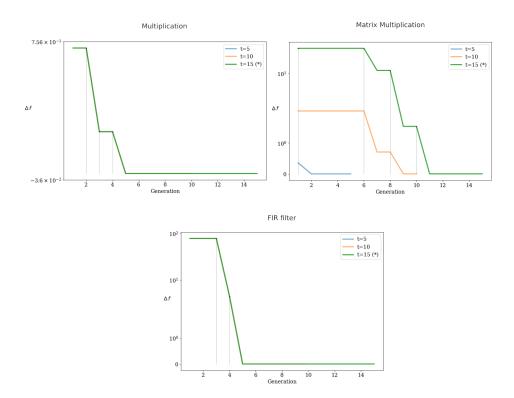

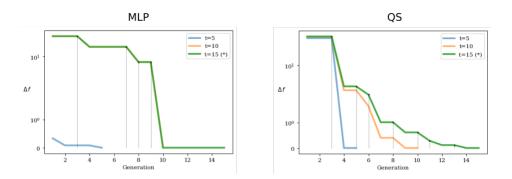

| 7.2  | Running metric. Convergence EMO DSE for basic applications.                              |     |

| 7.3  | Running metric. Convergence EMO DSE for highly demanding applications.                   |     |

| 7.4  | Objective space EMO DSE for basic applications.                                          |     |

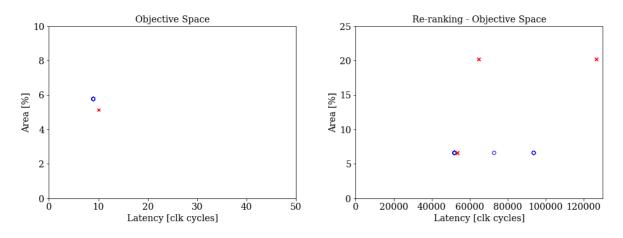

| 7.5  | Objective space EMO DSE for MLP and pre-ranking algorithms.                              | 113 |

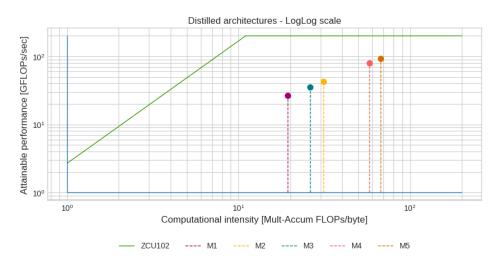

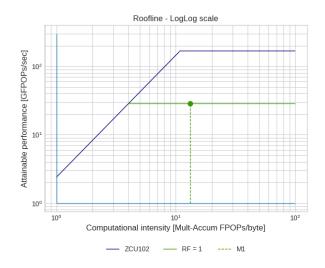

| 8.1  | Roofline model for MLP-based models targeting ZCU102 platform.                           | 120 |

| 8.2  | Roofline model for MLP M1 model 32-bit fixed-point precision, targeting ZCU102           |     |

|      | platform.                                                                                | 121 |

| 8.3 | Roofline model for MLP M1 model 32-bit fixed-point precision, targeting ZCU102 |

|-----|--------------------------------------------------------------------------------|

|     | platform. Reuse factor impact in the attainable performance                    |

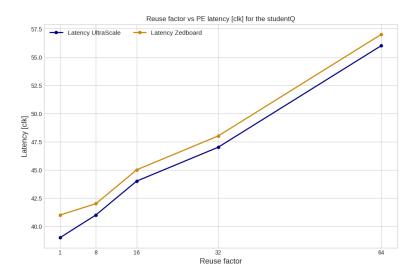

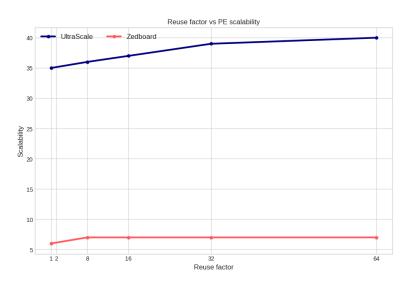

| 8.4 | Reuse factor vs latency for MLP architecture                                   |

| 8.5 | Reuse factor vs scalability for MLP architecture                               |

# List of Tables

| 3.1 | Features of the computing models PRAM, BSP, LogP, CCM, multi-BSP, and DRAM-            |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | only Roofline.                                                                         | 37 |

| 4.1 | Contributions presented in the literature for performance estimation. The acronyms     |    |

|     | used in the table are: A: area, L: latency, P: power consumption, QoR: quality of re-  |    |

|     | sult, C: communication, T: throughput, E: energy, S: speed-up, RT: reconfiguration     |    |

|     | time, S-C: SystemC, I-C: Impulse C, HDL: hardware description language, MH: meta-      |    |

|     | heuristics, Em: empirical, and PN: Petri Nets.                                         | 49 |

| 4.2 | Models used for FPGA/SoC on different research areas.                                  | 54 |

| 4.3 | Utilization of frameworks FPGA/SoC on different research areas. PDR: Partial dy-       |    |

|     | namic reconfiguration                                                                  | 57 |

| 5.1 | Resource and latency estimation for the basic operations obtained through HLS tool.    | 62 |

| 5.2 | Pipeline directive: resource estimation for 32-bit fixed point, obtained through HLS   |    |

|     | tool. From left to right: number of DSP, FF and LUT due to expressions (expDSP,        |    |

|     | expFF, expLUT), LUT consumed by multiplexers (muxLUT), LUT and FF used as reg-         |    |

|     | isters (regLUT, regFF), total number of operations (Nop), trip count (TC), number of   |    |

|     | each operation inside the loop (Add, Mult, Sub, Div), total number of expressions      |    |

|     | (NopExp).                                                                              | 63 |

| 6.1 | Distilled architectures based on MLP.                                                  | 80 |

| 6.2 | Distilled architectures based on MLP. The four classes of pulse are represented by c0, |    |

|     |                                                                                        |    |

| 6.3 | HLS reports for M1 MLP @200MHz, without AXI interface. Latency in clock cycles.                    |                |

|-----|----------------------------------------------------------------------------------------------------|----------------|

|     | RF: reuse factor (configuration option in hls4ml). For ZCU102 and PYNQ-Z1, the re-                 |                |

|     | ports were obtained with Vivado HLS 2019.2.1. For the KRIA device, the report was                  |                |

|     | obtained from Vitis HLS 2021.1.1.                                                                  | 33             |

| 6.4 | Place & route report for the KRIA device. From Vivado 2021.1.1.                                    | 33             |

| 6.5 | Metric estimations for KRIA device, obtained from Vivado 2021.1.1. P & R stands for                |                |

|     | place & route.                                                                                     | 34             |

| 6.6 | Complete system. Utilization from P & R reports (post-implementation). Reports                     |                |

|     | were obtained with Vivado 2021.1.1.                                                                | 38             |

| 6.7 | Isolated inference IP core. Utilization from P & R reports (post-implementation). Re-              |                |

|     | ports were obtained with Vivado 2021.1.1.                                                          | 38             |

| 6.8 | Re-ranking algorithm - 32-bits floating-point version. Latency in clock cycles. The                |                |

|     | acronyms used in the table are: HD: Hardware design. [A]QS 100 Trees. No directives.               |                |

|     | [B]. QS 1000 Trees. No directives. Reports obtained through Vivado HLS 2019.1.1.                   | <del>)</del> 2 |

| 6.9 | Re-ranking algorithm. From [A] to [D] with binning and quantization strategies; [E]                |                |

|     | to [F] 32 floating-point version. Latency in clock cycles. The acronyms used in the                |                |

|     | table are: HD: Hardware design. [A]. No directives. Base implementation. [B]. No                   |                |

|     | directives. One fixed loop [C]. No directives. Loop MC_L divided by a factor of four.              |                |

|     | [D]. Same case as [C], but with directives applied. [E]. Floating-point with code re-              |                |

|     | structuring. No directives. [F]. Floating-point with Loop MC_L divided by a factor of              |                |

|     | four and directives                                                                                | <del>)</del> 4 |

| 7.1 | Available resources on Kria KV260 development board                                                | 97             |

| 7.2 | Metric estimation through HLS tool and MARTE for multiplication. The acronyms                      |                |

|     | used in the table are: HD: Hardware design. A. No directives. [B] Unroll and array                 |                |

|     | partition complete. [C] Pipeline II=1                                                              | 00             |

| 7.3 | $P_{error}$ , $AD_L$ , and $L_{ratio}$ for multiplication. The acronyms used in the table are: HD: |                |

|     | Hardware design. [A]. No directives. [B] Unroll and array partition complete. [C]                  |                |

|     | Pipeline II=1                                                                                      | 00             |

| 7.4  | Metric estimation through HLS tool and MARTE for matrix multiplication. The acronyms                 |

|------|------------------------------------------------------------------------------------------------------|

|      | used in the table are: HD: Hardware design. [A]. No directives. [B] AP + Product Loop:               |

|      | Pipeline II=3. [C] AP + Col Loop: Pipeline II=3. [D]. AP + Row Loop: Unroll Factor=2                 |

|      | [E]. AP + Row Loop: Pipeline Factor=3                                                                |

| 7.5  | $P_{error}$ , $AD_L$ , $L_{ratio}$ and for matrix multiplication. The acronyms used in the table     |

|      | are: HD: Hardware design. [A]. No directives. [B] AP + Product Loop: Pipeline II=3.                  |

|      | [C] AP + Col Loop: Pipeline II=3. [D]. AP + Row Loop: Unroll Factor=2 [E]. AP + Row                  |

|      | Loop: Pipeline Factor=3                                                                              |

| 7.6  | Metric estimation through HLS tool and MARTE for FIR filter. The acronyms used                       |

|      | in the table are: HD: Hardware design. [A]. No directives. [B]. Pipeline II = 3, [C].                |

|      | Pipeline II = 5, [D]. Pipeline II = 3 + AP complete                                                  |

| 7.7  | $P_{error}$ , $AD_L$ , and $L_{ratio}$ for FIR filter. The acronyms used in the table are: HD: Hard- |

|      | ware design. [A]. No directives. [B]. Pipeline II = 3, [C]. Pipeline II = 5, [D]. Pipeline II        |

|      | = 3 + AP complete                                                                                    |

| 7.8  | Metric estimation through HLS tool and MARTE for pulse shape discriminator. The                      |

|      | acronyms used in the table are: HD: Hardware design. [A]. 8-bits fixed-point, reuse                  |

|      | factor = 1                                                                                           |

| 7.9  | $P_{error}$ , $AD_L$ , and $L_{ratio}$ for pulse shape discriminator. The acronyms used in the       |

|      | table are: HD: Hardware design. [A]. Reuse factor = 1,                                               |

| 7.10 | Pulse shape discriminator. Perror considering MARTE estimation and place and                         |

|      | route report (Vivado 2021.1.1)                                                                       |

| 7.11 | Metric estimation through HLS tool and MARTE for automatic pest classification al-                   |

|      | gorithm. The acronyms used in the table are: HD: Hardware design. [A]. Reuse factor                  |

|      | = 1                                                                                                  |

| 7.12 | $P_{error}$ , $AD_L$ , and $L_{ratio}$ for pest classification algorithm. The acronyms used in the   |

|      | table are: HD: Hardware design. [A]. Reuse factor = 1                                                |

| 7.13 | Automatic pest classification. $P_{error}$ considering MARTE estimation and P & R re-                |

|      | port (Vivado 2021.1.1)                                                                               |

| 7.14 Metric estimation through HLS tool and MARTE for re-ranking algorithm. The acronyms                 |

|----------------------------------------------------------------------------------------------------------|

| used in the table are: HD: Hardware design. [A]. No directives. [B]. Pipeline II=12                      |

| (loop 1.1) [C]. Pipeline II=12 (loop 1.1) + Pipeline II=6 (loop 2) + Array Partition com-                |

| plete                                                                                                    |

| 7.15 $P_{error}$ , $AD_L$ , and $L_{ratio}$ re-ranking algorithm. The acronyms used in the table are:    |

| HD: Hardware design. [A]. No directives. [B]. Pipeline II=12 (loop 1.1) [C]. Pipeline                    |

| II=12 (loop 1.1) + Pipeline II=6 (loop 2) + Array Partition complete                                     |

| 7.16 Re-ranking (implementation of [B] option from Table 7.14). $P_{error}$ considering MARTE            |

| estimation and P & R report (Vivado 2021.1.1)                                                            |

| 7.17 Configurations provided by MARTE DSE based on single-objective BO for latency                       |

| optimization. The acronyms are: D=0 No directive, D=1 Pipeline, D=2 Unroll, AP:                          |

| array partition.                                                                                         |

| 7.18 MARTE EMO DSE efficient configurations. The acronyms are: D=0 No directive, D=1                     |

| Pipeline, D=2 Unroll, AP: array partition                                                                |

| 7.19 Runtime measured in seconds. HLS single execution with directives. Single-objective                 |

| BO with stopping-criterion 100 iterations.                                                               |

| 7.20 Available resources on ZCU102 development board                                                     |

| 7.21 Comparison results between MARTE and Vivado HLS 2019.1.1, targetting xczu9eg-                       |

| ffvb1156-2-e part. The acronyms used in the table are: HD: Hardware design. Multi-                       |

| plication: [A]. No directives, [B] AP + Unroll. [C] Pipeline II=1, Matrix Multiplication:                |

| [D]. No directives. [E]. Pipeline II=3 (Loop: Col) + AP. [F]. Pipeline II=3 (Loop: Row) +                |

| AP. <b>FIR filter:</b> [G]. No directives. [H]. Pipeline II = 3 + AP complete. [I]. Pipeline II = 3. 115 |

| 7.22 $P_{error}$ , $AD_L$ , and $L_{ratio}$ for the basic applications considering MARTE and Vivado      |

| HLS 2019.1.1. The acronyms used in the table are: HD: Hardware design. Multiplica-                       |

| tion: [A]. No directives, [B] AP + Unroll. [C] Pipeline II=1. Matrix Multiplication: [D].                |

| No directives. [E]. Pipeline II=3 (Loop: Col) + AP. [F]. Pipeline II=3 (Loop: Row) + AP.                 |

| <b>FIR filter:</b> [G]. No directives. [H]. Pipeline II = 3 + AP complete. [I]. Pipeline II = 3 116      |

|                                                                                                          |

# List of acronyms

| Α                        | Area                                                                                                        |

|--------------------------|-------------------------------------------------------------------------------------------------------------|

| ADRS                     | Average distance from reference set                                                                         |

| AF                       | Array factor                                                                                                |

| ANN                      | Artificial neural network                                                                                   |

| AP                       | Attainable performance                                                                                      |

| ASIC                     | Application specific integrated circuit                                                                     |

| AUC                      | Area under the curve                                                                                        |

| BBO                      | Black-box optimization                                                                                      |

|                          |                                                                                                             |

| BRAM                     | Block RAM                                                                                                   |

| BRAM<br>BO               | Block RAM<br>Bayesian optimization                                                                          |

|                          |                                                                                                             |

| во                       | Bayesian optimization                                                                                       |

| BO<br>BSP                | Bayesian optimization<br>Bulk synchronous parallel                                                          |

| BO<br>BSP<br>CCM         | Bayesian optimization<br>Bulk synchronous parallel<br>Collective computing model                            |

| BO<br>BSP<br>CCM<br>CDFG | Bayesian optimization<br>Bulk synchronous parallel<br>Collective computing model<br>Control data flow graph |

### List of acronyms

| CNN  | Convolutional neural network              |

|------|-------------------------------------------|

| CR   | Cosmic rays                               |

| CRCW | Concurrent read concurrent write          |

| CREW | Concurrent read exclusive write           |

| CUDA | Compute Unified Device Architecture       |

| D    | Design space                              |

| DAQ  | Data acquisition systems                  |

| DDDG | Dynamic data dependence graph             |

| DMA  | Direct memory access                      |

| DNN  | Deep neural network                       |

| DSE  | Design space exploration                  |

| DSP  | Digital signal processor                  |

| EA   | Evolutionary algorithm                    |

| EI   | Expected improvement                      |

| ЕМО  | Evolutionary multi-objective optimization |

| ERCW | Exclusive read concurrent write           |

| EREW | Exclusive read exclusive write            |

| ERT  | Empirical Roofline toolkit                |

| FF   | Flip-Flop                                 |

| FIR  | Finite impulse response                   |

| FPGA | Field programmable gate array             |

| GNN  | Graph neural networks                     |

### List of acronyms

| GP      | Gaussian process                                      |

|---------|-------------------------------------------------------|

| HDL     | Hardware description language                         |

| HLS     | High-level synthesis                                  |

| НРС     | High-performance computing                            |

| HPM     | Hierarchical model for parallel computations          |

| HVE     | Hypervolume error                                     |

| II      | Initiation interval                                   |

| I/O     | Input/Output                                          |

| IL      | Iteration latency                                     |

| ІоТ     | Internet of things                                    |

| IP      | Intellectual property                                 |

| IR      | Intermediate representation                           |

| KD      | Knowledge distillation                                |

| L       | Latency                                               |

| L1      | Level-1 cache memory                                  |

| L2      | Level-2 cache memory                                  |

| LAGO    | The Latin American Giant Observatory                  |

| LLVM IR | Low-level virtual machine intermediate representation |

| LUT     | LookUp Table                                          |

| ML      | Machine learning                                      |

| MLP     | Multi-layer perceptro                                 |

| MOOA    | Multi-objective optimization algorithms               |

| MPSoC   | Multiprocessor system on chip                   |

|---------|-------------------------------------------------|

| NN      | Neural network                                  |

| NSGA-II | Elitist non-dominated sorting genetic algorithm |

| P & R   | Place and route                                 |

| РС      | Peak computation                                |

| PE      | Processing element                              |

| PF      | Pareto-optimal frontier                         |

| PI      | Probability of improvement                      |

| РМВ     | Peak memory bandwidth                           |

| PRAM    | Parallel random access machine                  |

| PSD     | Pulse shape discriminator                       |

| QAP     | Quantization-aware pruning                      |

| QAT     | Quantization-aware training                     |

| QoR     | Quality of results                              |

| QS      | QuickScorer                                     |

| RAM     | Random access machine                           |

| ROC     | Receiver operating characteristics              |

| RTL     | Register transfer level                         |

| SC      | scalability                                     |

| SIMD    | Single Instruction/Multiple Data                |

| SoC     | System on chip                                  |

| SPMD    | Single program multiple data                    |

| Т   | Throughput                                    |

|-----|-----------------------------------------------|

| тс  | Trip count                                    |

| UF  | Unrolling factor                              |

| UMH | Uniform Memory Hierarchy Model of Computation |

| WCD | Water Cherenkov detectors                     |

## **Chapter 1**

## Introduction

### 1.1 Motivation

Nowadays, the development of algorithms focuses on performance-efficient and energy-efficient computations. Technologies such as field programmable gate array (FPGA) and system on chip (SoC) based on FPGA (FPGA/SoC) [2–5] have shown their ability to accelerate intensive computing applications while saving power consumption, owing to their capability of high parallelism and reconfiguration of the architecture.

Several high-level synthesis (HLS) tools [6] have been proposed by vendors and academics, such as Vivado HLS [7], formerly AutoPilot [8], Intel HLS [9], LegUp [10], Bambu [11], and others [12]. These tools facilitate the adoption of FPGAs in different fields, as they allow the creation of a register transfer level (RTL) code from a high level of abstraction. Nevertheless, the efficient use of these technologies usually requires the knowledge of the underlying hardware and code restructuring techniques in the original algorithm [13]. This is a time-consuming task for algorithm designers who want to take advantage of the inherent characteristics of these reconfigurable technologies.

HLS tools support C/C++, SystemC, and OpenCL [14] codes to generate the final RTL code.

This chapter is based on the work published in [1]: **Molina, R.S.**; Gil-Costa, V.; Crespo, M. L; Ramponi, G. (2022) "High-Level Synthesis Hardware Design for FPGA-based Accelerators: Models, Methodologies, and Frameworks". In IEEE Access, vol. 10, pp. 90429-90455, 2022. IEEE.

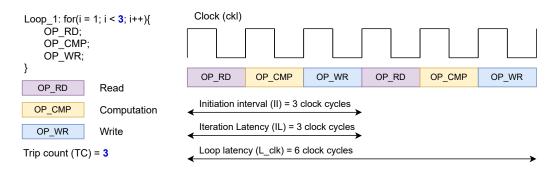

These tools provide the designer with a detailed report for each algorithmic solution, including information about the estimation of latency, resource utilization (also known as the area occupied), and throughput. The use of directives allows code optimization through parallel techniques, such as loop pipelining, loop unrolling, array partitioning, and array reshaping. For each solution, the designer can specify different combinations of directives; comparing the reports provided by these tools, the best option can be determined according to different performance metrics.

Furthermore, these tools allow a design space exploration (DSE), which involves the evaluation of multiple implementations with different combinations of user design constraints, FPGA features, and directives, also known as knobs or optimizations. Setting these optimizations to obtain a hardware design with the desired characteristics is a problem that grows exponentially with the number of directives the user adds and complex code structures. The generated hardware is directly associated with the applied directives, but sometimes applying and tuning directives requires considerable effort to obtain a proper hardware implementation. An optimal DSE process grants a hardware design with a good compromise between metrics such as latency, area, throughput, and power consumption.

Over the years, parallel computing models have proven their benefits across different architectures, such as clusters of distributed processors with single cores and multicores, GPU, and cloud. These models act as a bridge between the architecture and the software developer. The actual trend in parallel computer architectures demonstrates progress toward hybrid architectures combining many cores, superscalars, SIMD, hardware accelerators, and on-chip communication systems, which require handling computations and data locality at several levels to achieve suitable performance [15].

Using computing models, methodologies, and frameworks to predict the performance of FP-GA/SoC architectures may reduce design times and improve productivity, which are critical issues when choosing these architectures.

Currently, the existing design cycles for FPGA-based reconfigurable architectures are long, owing to the complexity of the architecture and the different applications in multiple research areas. Therefore, for all of the above, a methodology that includes a performance estimation model and exploration of the design space is necessary to analyze the system for its subsequent implementation in hardware.

Applications in the field of image analysis are a relevant research focus in the scientific com-

2

munity [16–18]. The growth of artificial vision techniques for the processing, recognition, and classification of images has made it possible to expand the expectations of systems to solve problems that are otherwise much more difficult or impossible in different areas, such as security, industry, and autonomous driving.

As presented in [1], in recent years, machine learning (ML) techniques have been applied in multiple fields such as fluid dynamics, high-energy physics, information retrieval, image processing, video processing, security, and biology [19–21]. Because of this trend, models for FPGA-based architectures are being developed to accelerate ML applications with efficient exploitation of hardware resources to improve productivity in the design phase [22–24].

Therefore, to evaluate this thesis proposal, the chosen applications are in the context of image analysis, high-energy physics, and information retrieval.

### 1.2 Hypothesis

It is possible to develop a methodology for FPGA/SoC architectures composed of analytical models and integrated with a DSE engine based on mathematical programming, guiding the exploration process through HLS rules, to estimate performance metrics, while improving the productivity of the hardware developers.

### 1.3 Objectives

This thesis aims to efficiently develop, deploy, and evaluate image analysis and highly demanding applications on SoC-based FPGA. Therefore, this research proposes using a methodology, algorithms, and associated software tools for FPGA/SoC hardware acceleration, including a performance estimation model for applications deployed on reconfigurable hardware accelerators based on FPGA.

The estimated metrics include latency and resource utilization. Moreover, a design space explorer engine is incorporated to provide a set of hardware designs that satisfy the design conditions defined by the hardware designer.

3

#### 1.3.1 Specific objectives

- Exploration, proposal, and development of performance models for FPGA/SoC to estimate mainly latency and resource utilization.

- Investigation, proposal, and development of a methodology for the exploration of the design space for FPGA.

- Implementation of highly demanding applications on FPGA/SoC, including pulse shape discriminator for cosmic rays based on ML, deep neural networks for automatic image classification, and re-ranking for information retrieval.

### 1.4 Contribution

The contributions of this thesis are as follows:

- MARTE as a comprehensive performance estimator for hardware acceleration, composed of analytical models to estimate area and latency and a DSE engine for providing high-level insights to hardware developers

- MARTE DSE engine, compound of two independent sub-engines:

- DSE single-objective Bayesian optimization for latency.

- DSE evolutionary multi-objective optimization for latency-area.

- Integration of MARTE with the Roofline model, the leading parallel computing model adapted for FPGAs.

- An exhaustive evaluation of a methodology to deploy deep neural networks classifier on SoC/FPGA.

- Hardware acceleration of:

- A pulse shape discriminator for cosmic rays to be paired with a front-end data-acquisition system based on SoC-FPGAs for water Cherenkov detectors (WCD).

- Automatic pest classification based on convolutional neural networks (CNN).

- Re-ranking algorithm for information retrieval.

### 1.5 Methodology

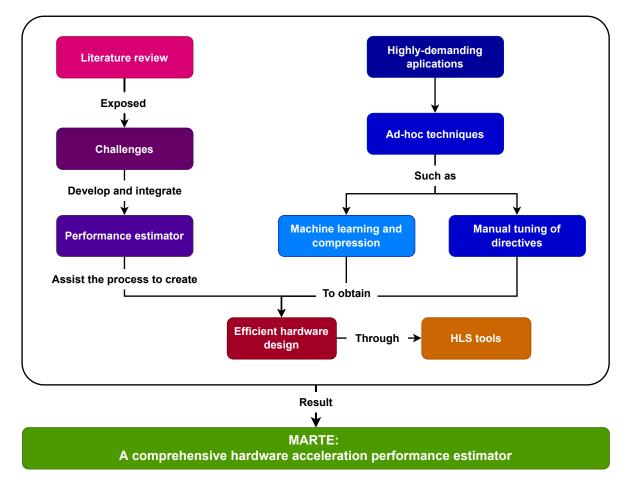

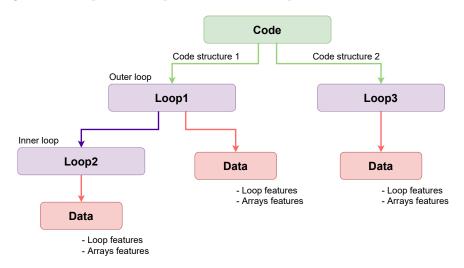

Fig. 1.1 presents the methodology proposed in this thesis to address the gap between applications and FPGA/SoC architectures and, in turn, obtain an efficient hardware design for image analysis and highly demand applications using the HLS tool. Two complementary strategies are considered:

Figure 1.1: Methodology.

- **Performance estimator:** the literature review shows that existing performance estimators based on models, methodologies, and frameworks proposed for FPGA/SoC still need to overcome different challenges to be widely used for estimating system performance in the early stages of design. Moreover, this type of tool could assist the hardware developer in the process of creating efficient hardware designs.

- Ad-hoc techniques: an efficient hardware design can be obtained by combining different

techniques to satisfy the user and system constraints. These techniques can be related to the application or tool domains. The former includes the use of methods such as ML, compression, and efficient algorithms to map applications on FPGA/SoC. The latter is based on the options offered by the HLS tool, such as compiler directives, which require considerable effort to obtain a suitable configuration to improve the throughput, latency, and resource utilization.

To overcome the exposed above, MARTE, a comprehensive performance estimator for hardware acceleration is proposed to effectively predict the resource utilization and latency for FPGA/-SoC, building a bridge between the application and architectural domains. Furthermore, image analysis and other highly demanding applications (such as automatic pest classification, pulse shape discriminator for cosmic rays, and re-ranking for information retrieval) are considered in this thesis to achieve the objectives, emphasizing the benefits when this type of application is traversed by compression techniques when targeting FPGA/SoC devices.

Regarding the application object in this thesis, different problems are explored in relevant areas, considering highly demanding applications:

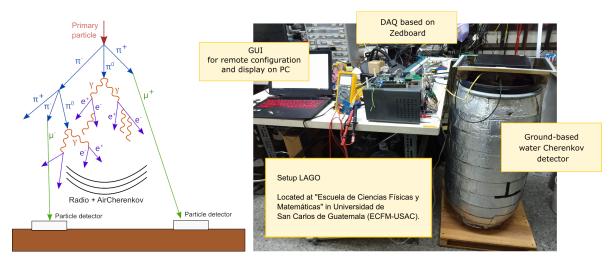

- **Pulse shape discrimination:** data-driven learning based on neural network (NN) models for pulse shape discriminator (PSD) in the context of Water Cherenkov detectors (WCD) used in LAGO (The Latin American Giant Observatory) experiment [25], aiming to perform pulse discrimination in a front-end data-acquisition system based on FPGA/SoC. The PSD identifies four types of pulses (based on the shape) obtained from the corresponding data acquisition system.

- **Image classification:** automatic pest classification based on ML to be deployed in an embedded system, considering two types of classes: insects and the corresponding plague (moth).

- **Re-ranking algorithm:** exploitation of the parallelism on FPGA/SoC devices for the re-ranking algorithm QUICKSCORER (QS), the state of the art algorithm for performing fast inference with tree ensembles [26, 27]. QS exploits a particular representation of the tree ensemble based entirely on linear arrays accessed with high locality. This characteristic permits a very fast traversal of the tree ensemble at inference time.

### 1.6 Challenges

Nowadays, the explosive growth of accelerators promises greater computational capabilities. FP-GA/SoC devices are widely used as hardware accelerators in different areas of research and development. However, there is the necessity to address some challenges, as presented in [1]. Even using HLS tools, reconfiguring an SoC-based FPGA with an efficient hardware design is a challenging task. This is easily made apparent by some observations [1]:

- Physical resources, such as memory bandwidth, reconfigurable hardware (LUTs, CLBs, and slices), and static hardware (DSPs and BRAMs) are limited in FPGA/SoC devices. Thus, the available physical resources should be used skillfully, considering techniques to improve the latency, area, and power.

- Code restructuring techniques aid in creating efficient FPGA implementations using HLS tools, modifying the source code of the application according to the FPGA architecture.

- The number of processing elements (PE) in a hardware design, and consequently the level of coarse-grain parallelism that can be obtained, is limited to the available physical resources. Therefore, different strategies should be implemented to exploit the architecture to increase the system's scalability.

- There is a trade-off between the different metrics to be optimized. For example, the area occupied is likely to increase if the latency is reduced, and vice versa. Thus, the FPGA designer should choose a good compromise between the metrics in terms of resources, computing operations, and throughput, among others.

- The hardware generated through HLS tools is directly associated with the applied directives, but sometimes applying and tuning directives require considerable endeavour to obtain a proper FPGA implementation. Moreover, generating a solution for each directive combination is associated with the synthesis time, reducing productivity.

- The exploration of the design space is linked to the human effort of performing combinations of directives, user design constraints, FPGA features, and code restructuring, among others.

Hardware designers can cope with the above considerations through performance estimators to reduce design time, as follows:

- The coarse-grain parallelism level can be obtained by employing a Roofline model, identifying the computation-to-communication ratio, and exposing the relationship between communication bottlenecks, computations, and the number of replicas.

- Design space explorers aim to identify the optimal combination of directives to obtain an HLS-based hardware design with a proper trade-off among different metrics, generating the Pareto-optimal set of designs. Reducing the design space and avoiding HLS in the exploration process can improve the design time.

- Models integrated within a methodology or framework can automatically estimate the performance of HLS-based hardware designs without executing HLS tools.

- Some frameworks and methodologies including DSE provide automatic directive-insertion optimizations and code transformation insights.

Nevertheless, the literature review shows that a number of challenges has to still be addressed in order to make optimal use of performance estimators (models, methodologies, and frameworks) such as:

- Recent HLS tools generate more comprehensive reports with more accurate information on total resource availability, latency, clock frequency, and resource utilization. These reports can be integrated with models, methodologies, and frameworks to estimate metrics and provide an initial value for the replication factor of a single PE. However, the report generation is linked to the synthesis time of the FPGA implementation. Reducing the design time is essential when using FPGA/SoC without losing hardware quality to reconfigure the platform. Thus, if the HLS tool is in the loop for performance estimation using reports, it can lead to an increased design time.

- The performance metrics reported by HLS tools make them suitable to be combined with a parallel computation model to reduce the time required to obtain the necessary statistics for each implementation for a specific application. However, there is a gap between the HLS report and the real hardware implementation that can be addressed with a performance model that includes the results obtained from the sourceCode-to-bitstream flow using the values related to final hardware utilization, power consumption, and timing reports.

- Computing models for FPGA-based reconfigurable hardware accelerators have to consider that the inherent hardware is not fixed. Rather, it is defined by how the application is described. Therefore, a higher number of parameters have to be included in the model, such as hardware resources (DSP, BRAM, LUT, and FF), programmable logic clock, latency, byte-operations (Bops), scalability in the number of PE, and power consumption. This contrasts with the computing models proposed for other parallel platforms, such as PRAM or BSP, that use a few parameters. Nevertheless, including more parameters in the model increases the analysis accuracy but affects the complexity of the model analysis. Therefore, the trade-off between these two features has to be addressed. In addition, the parameters should be adjusted according to the particular combination of directives applied to the source code.

- The compatibility among different versions of HLS tools is not granted by models, methodologies, and frameworks. As a consequence, calibration techniques can help maintain compatibility between high-level tools, thereby avoiding being tied to one version of HLS tool in particular [28].

Moreover, when a DSE engine is integrated with models, methodologies, and frameworks, the following aspects need to be considered:

- One of the key points in the DSE is the execution of HLS tools during the exploration stage to validate the configuration obtained. This behaviour can lead to a long runtime, becoming a drawback in the DSE phase. Therefore, the adoption of different techniques to reduce the execution time of the exploration phase is indispensable.

- It is often sufficient to find a suboptimal combination of knobs based on specific metrics and user constraints. An important strategy is pruning the design space using intermediate Pareto-optimal designs, giving priority to the points that permit high-performance behaviours.

- The DSE engine should guarantee a good compromise among the QoR and performance metrics.

- Approximate computing [29] can lead to an expansion of the design space, generating Paretooptimal designs with a trade-off between area-power-latency estimation and error compu-

tation. A reduction in the space to be explored is fundamental to minimizing the invocations of HLS tools.

- It is important to identify the strengths and weaknesses of a given design space explorer. This can be performed using benchmarks.

- Mapping an optimal design from the DSE to the FPGA/SoC can be challenging while maintaining the QoR reported by the DSE engine, mainly latency. In the process of mapping the final hardware design onto the FPGA/SoC, the place-and-route phase plays an important role and different strategies provided by commercial tools can be used in this phase, adding another factor to be analyzed.

- It is fundamental to consider the application of HLS-specific compiler optimizations, due to the impact that they have on the hardware quality, in terms of latency, area, and power consumption [30].

### 1.7 Scientific publications

This research has generated the following original scientific contributions:

#### Thesis related

- Molina, R.S., Gil-Costa, V., Crespo, M. L, Ramponi, G. (2022) "High-Level Synthesis Hardware Design for FPGA-based Accelerators: Models, Methodologies, and Frameworks". In IEEE Access, vol. 10, pp. 90429-90455, 2022. IEEE.

- Molina, R. S., Carrer. V., Ballina; M., Crespo, M. L., Bollati, L., Sequeiro, D., Marsi, S. Ramponi, G. (2022) "ML-based classifier for precision agriculture on embedded systems". In International Conference on Applications in Electronics Pervading Industry, Environment and Society [Accepted].

- Gil-Costa, V., Loor, F., Molina, R.S., Nardini, F. M., Perego, R., Trani, S. (2022) "Energy-Efficient Ranking on FPGAs through Ensemble Model Compression". In 12th Italian Information Retrieval Workshop.

- Molina, R. S., Garcia, L. G., Morales, I. R., Crespo, M. L., Ramponi, G., Carrato, S., Cicuttin, A., Perez, H. (2022). "Compression of NN-Based Pulse-Shape Discriminators in Front-End Electronics for Particle Detection". In International Conference on Applications in Electronics Pervading Industry, Environment and Society, pp. 93-99. Springer, Cham.

- Gil-Costa, V., Loor, F., Molina, R. S., Nardini, F. M., Perego, R., Trani, S. (2022). "Ensemble Model Compression for Fast and Energy-Efficient Ranking on FPGAs". In European Conference on Information Retrieval, pp. 260-273. Springer, Cham.

- Suárez, A., Molina, R. S., Ramponi, G., Petrino, R., Bollati, L., Sequeiros, D. (2021, November). "Pest detection and classification to reduce pesticide use in fruit crops based on deep neural networks and image processing". In 2021 XIX Workshop on Information Processing and Control (RPIC), pp. 1-6. IEEE.

- Molina, R. S., Loor, F., Gil-Costa, V., Nardini, F. M., Perego, R., Trani, S. (2021). "Efficient traversal of decision tree ensembles with FPGAs". In Journal of Parallel and Distributed Computing, 155, 38-49. Elsevier.

- García Ordóñez, L. G., Molina, R. S., Morales Argueta, I. R., Crespo, M. L., Cicuttin, A., Carrato, S., Ramponi, G., Pérez Figueroa, H. E., Ballina Escobar, M. G. (2021). "Pulse shape Discrimination for Online Data Acquisition in Water Cherenkov Detectors Based on FPGA/SoC". In 37th International Cosmic Ray Conference (ICRC2021), p. 274. PoS Sissa.

- Marsi, S., Bhattacharya, J., Molina, R. S., Ramponi, G. (2021). "A Non-Linear Convolution Network for Image Processing". In Electronics 2021, 10, 201. MDPI.

- Garcia, L. G., Molina, R. S., Crespo, M. L., Carrato, S., Ramponi, G., Cicuttin, A., Morales, I. R. Perez, H. (2021). "Muon–Electron Pulse Shape Discrimination for Water Cherenkov Detectors Based on FPGA/SoC". Electronics 2021, 10, 224. MDPI.

- Guzzi, F., De Bortoli, L., **Molina, R. S.**, Marsi, S., Carrato, S., Ramponi, G. (2020). "Distillation of an End-to-End Oracle for Face Verification and Recognition Sensors". In Sensors, 20(5), 1369. MDPI.

#### Others

- Cicuttin, A., Morales, I. R., Crespo, M. L., Carrato, S., García, L. G., Molina, R. S., Valinoti, B., Folla Kamdem, J. (2022). "A Simplified Correlation Index for Fast Real-Time Pulse Shape Recognition". In Sensors, 22(20), 7697. MDPI.

- Florian Samayoa, W., Valinoti, B., Molina, R. S., Garcia Ordonez, L. G., Crespo, M. L., Carrato, S., Cicuttin, A., Levorato, S. (2022). "Diagnostic analytics for pixelated particle detectors: A case study". In International Conference on Applications in Electronics Pervading Industry, Environment and Society [Accepted].

- Crespo, M. L., Foulon, F., Cicuttin, A., Bogovac, M., Onime, C., Sisterna, C., Melo, R., Florian Samayoa, W., García Ordóñez, L. G., Molina, R. S., Valinoti, B. (2021). Remote Laboratory for E-Learning of Systems on Chip and Their Applications to Nuclear and Scientific Instrumentation. In Electronics, 10(18), 2191. MDPI.

- Guillermo, G. L., Crespo, M. L., Carrato, S., Cicuttin, A., Oswaldo, F. W., Molina, R. S., Valinoti, B. Levorato, S. (2021). "High Voltage Isolated Bidirectional Network Interface for SoC-FPGA Based Devices: A Case Study: Application to Micro-pattern Gaseous Detectors". In Applications in Electronics Pervading Industry, Environment and Society. Lecture Notes in Electrical Engineering, vol 738, pp. 280-285. Springer, Cham.

- Molina, R. S., Gonzalez, V., Benito, J., Marsi, S., Ramponi, G., Petrino, R. (2021). "Implementation of Particle Image Velocimetry for Silo Discharge and Food Industry Seeds". In Applications in Electronics Pervading Industry, Environment and Society. Lecture Notes in Electrical Engineering, vol 738, pp. 3-11. Springer, Cham.

#### Awards

Industry impact award: Gil-Costa, V., Loor, F., Molina, R. S., Nardini, F. M., Perego, R., Trani, S. (2022). "Ensemble Model Compression for Fast and Energy-Efficient Ranking on FPGAs". In European Conference on Information Retrieval, pp. 260-273. Springer, Cham.

### **1.8** Thesis outline

The thesis is composed of nine main chapters, introduced as follows:

- Chapter 2 discusses specific topics in ML and mathematical programming. Because the applications focused on in this thesis are based on ML and compression techniques for their implementation in hardware, the basic concepts, ML-based model compression techniques, and methodology to deploy deep neural network classifiers on FPGA/SoC are introduced. Mathematical programming concepts for single- and multi-objective optimizations, which are used for DSE engine implementation, are introduced.

- Chapter 3 describes the background of FPGA/SoC and parallel computing models for performance estimation. FPGA/SoC architecture is presented with DSE, the main metrics for this technology, and the techniques to improve latency, area, and delay. As a model for performance estimation is proposed in this thesis, the leading parallel computing models for performance estimation are introduced.

- Chapter 4 summarizes and discuss the state of the art in performance estimators for FPGAbased reconfigurable hardware accelerators, providing a classification in general approaches and DSE. Moreover, their use for highly-demanding applications is exposed.

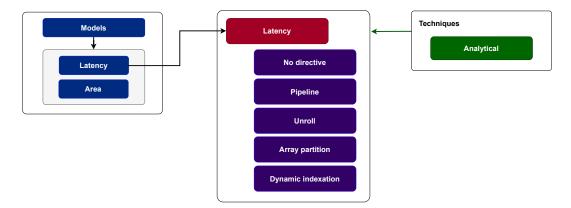

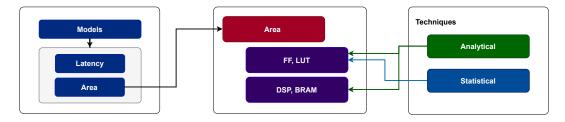

- Chapter 5 introduces MARTE, a comprehensive performance estimator for hardware acceleration through FPGA/SoC, composed by analytical models and a DSE engine based on single- and multi-objective optimizations. The different models are introduced as the techniques employed for their implementation.

- Chapter 6 presents the different cases of study and their corresponding hardware acceleration: pulse shape discriminator for cosmic rays, automatic pest classification, and re-ranking algorithm for information retrieval. The applications are traversed for an ensemble of compression techniques, to obtain a suitable implementation on FPGA/SoC.

- Chapter 7 discusses the performance evaluation of MARTE. The first stage of the experiments was aimed at evaluating MARTE with different applications (basic and highly demanding). In the second stage, the assessment of MARTE DSE engine is exposed, showing the efficiency and effectiveness of the engine to provide high-performance configurations.

- Chapter 8 provides a way to pair MARTE with the Roofline model, the leading parallel computing model adapted to FPGA architectures.

- Chapter 9 presents conclusions and future directions.

# **Chapter 2**

# Specific topics in machine learning and mathematical optimization

This chapter presents specific topics in machine learning (ML) and mathematical programming. Because the applications focused on in this thesis are based on ML and compression techniques for their implementation in hardware, Section 2.1 introduces the basic concepts, ML-based model compression techniques, and a methodology to compress ML architectures efficiently. Section 2.4 presents the concepts associated with mathematical programming for single- and multi-objective optimizations used for the DSE engine development and implementation.

# 2.1 Deep neural networks

Machine learning is a subfield of artificial intelligence (AI), and it aims to build analytical models based on data capable of learning and to improve performance [31]. Based on the learning process, ML techniques can be classified as supervised, semi-supervised, and unsupervised [32].

- **Supervised learning:** the algorithms are pre-trained on a fully labelled dataset. The main objective of this type of learning is predicting results from an input. In turn, classification and regression models can be found where the output of the function can be a numerical value (as in regression problems) or class label (as in classification problems).

- **Semi-supervised learning:** labelled (the least quantity) and unlabelled (the largest quantity) data are used during the training phase.

• **Unsupervised learning:** these algorithms do not have prior knowledge and aim to find patterns in the dataset, making it possible to organize them in some way. It is self-organized; there are only input data without labels and a cost function to be minimized.

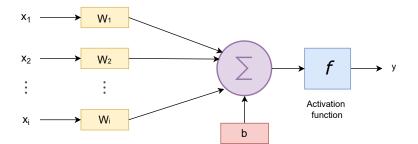

In supervised learning, an artificial neural network (ANN) [33] is composed of neuron (or node) interconnections arranged in different layers, usually an input layer, middle or hidden layers, and an output layer, where a prediction is generated. The connections between the neuron and inputs  $(x_i)$  are called weights  $(w_i)$ . Each node has several inputs and only one output, and the ANN uses a nonlinear activation function to compute the output value. This description is shown in Fig. 2.1 and is mathematically represented by Eq. (2.1).

$$y = f((\sum_{i} x_i w_i) + b)$$

(2.1)

where  $x_i$  are the inputs,  $w_i$  are the weights, *b* represents the bias, *f* the activation function and *y* the final output of the neuron.

Figure 2.1: Detail of a single neuron function.

In an ANN-based classifier, the input is mapped to a specific class. For this task, an ANN goes through a supervised training step to recognize patterns and compares its actual output with the desired output. The difference between these two values is adjusted with backpropagation.

Convolutional neural networks (CNN) are a type of deep neural network (DNN) that receives an image as input and extracts features directly from it, learning as the network trains on a collection of images. The architecture is defined through a stack of layers, and each layer transforms one volume of activation into another through a differentiable function. CNNs are mainly made up of two stages: feature extraction (composed of tens or hundreds of hidden layers based, mainly, on convolutional and pooling layers) and classification (based on fully-connected layers) [32]. For

more details in this topic, the reader can refer to [32].

DNNs are mainly composed of parameters and hyperparameters; the former are defined during training. The user defines the latter before training, characterizing the architecture by defining the number of layers and filters and the learning approach, among others. Techniques such as **random search** [34], **random grid** [35], and **Bayesian optimization** (BO) [36, 37] are mainly used for tuning the hyperparameters of DNNs, thereby avoiding the trial-error procedure for their selection [34, 38, 39]. Random search selects random trials and is a greedy approach that settles for local optimality, failing to end with global optimality. For a given hyperparameter space, grid search tries all the possible combinations of hyperparameters. BO is a sequential approach that uses the information from previous steps, scaling with the utmost resource utilization, handling noisy data well, and exploiting non-continuous spaces to attain global minima [40].

# 2.2 Compression for ML-based models

Compression techniques are essential for deploying machine learning models on resource-constrained devices while maintaining efficiency and effectiveness and obtaining smaller and faster models [41, 42].

Among the most commonly used techniques for compression are **pruning**, **quantization** [43], and **knowledge distillation** [44, 45], which can be combined to benefit the compression process with their unique characteristics. Pruning and quantization [42, 46] are orthogonal to distillation, helping to achieve better performance by reducing the size of the model with minimum loss of accuracy [47]. Pruning aims to reduce the number of parameters by removing neurons and connections, whereas quantization reduces the memory footprint by selecting the number of bits representing weights and biases.

Quantization-aware training (QAT) [42,48] and quantization-aware pruning (QAP) [49] are learning processes based on quantization methods. The former avoids post-training quantization, and the quantization operations on weights and activations are simulated while maintaining floatingpoint precision to update the weights and compute the gradient. The latter performs a QAT by integrating pruning.

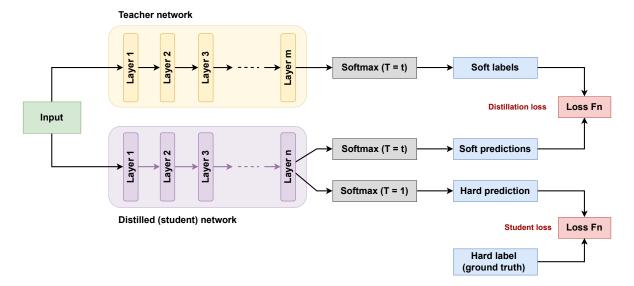

Finally, knowledge distillation (KD) [45] is devoted to transferring the knowledge (or "dark knowledge" according to Hinton) from a teacher network (a single large model or an ensemble

of models) to a smaller and faster target network (distilled or student) that can mimic the teacher's behavior, being computationally less expensive. Fig. 2.2 presents the process involved in KD. a

Figure 2.2: Knowledge distillation process.

In KD, the probability  $q_i$  of class *i* is calculated from the logits *z* as presented in Eq. 2.2, where *T* represents the temperature. The probability distribution obtained by the Softmax function becomes softer when *T* grows, providing more information, called by Hinton the "dark knowledge". If *T* = 1, the result is the same as the Softmax activation function [45].

$$q_{i} = \frac{e^{(\frac{z_{i}}{T})}}{\sum_{i} e^{(\frac{z_{j}}{T})}}$$

(2.2)

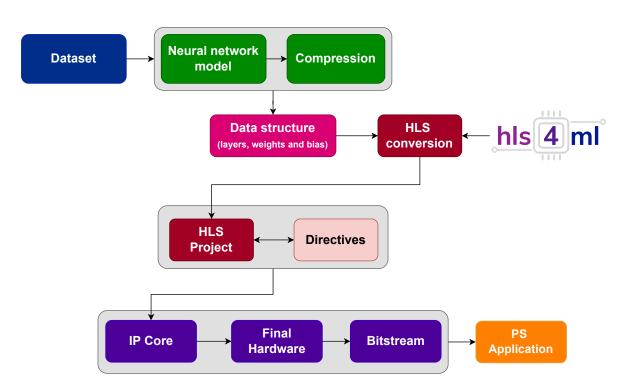

# 2.3 Methodology to deploy DNN-based classifiers on SoC

As the final goal is the implementation of an ML-based classifier in the FPGa/SoC platform, model compression is performed using an ensemble of different techniques: quantization, pruning, and KD. Fig. 2.3 shows the steps involved in the methodology used to obtain efficient compressed neural network-based classification models, supported by the literature in contributions such as [50, 51].

Figure 2.3: Methodology. The input is the labeled dataset used to train the teacher and student (or target) networks. After this, the data structure generated is the input for the hls4ml [52] package, translating the neural network-based model into a HLS project.

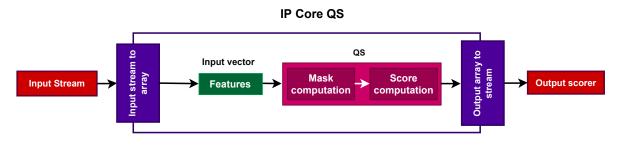

The input of the methodology is the labeled dataset used to train the target network. Then, the data structure generated is the input for the hls4ml package [52], translating the neural network-based model into an HLS project. Once the IP core is generated, it can be integrated with the final system (hardware and software).